在讨论ddr4内存时序之前,我们首先要了解什么是内存时序。简单来说,内存时序指的是内存模块中各个操作的时间间隔。这些操作包括读取数据、写入数据以及激活行等。内存时序的设置对于内存的性能和稳定性都有着非常重要的影响。

ddr4内存时序的意义

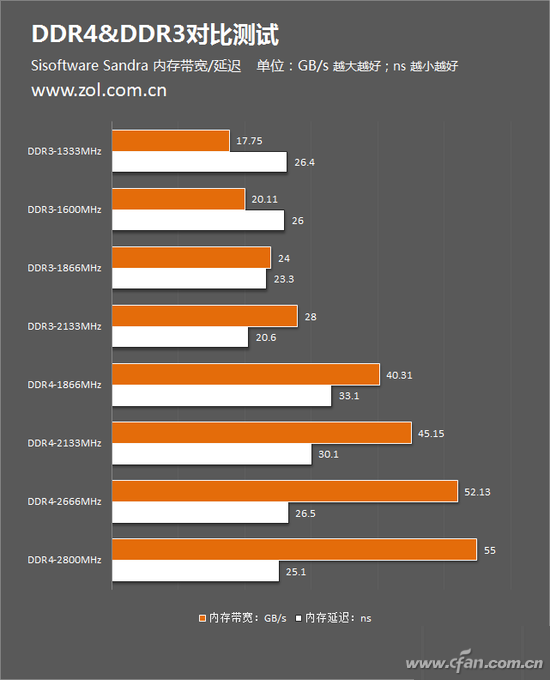

DDR4内存是目前市场上最新一代的内存标准,相较于之前的DDR3内存,在带宽和速度方面有了显著提升。然而,如果不正确地设置DDR4内存的时序,就无法充分发挥其潜力。

读取数据的时序

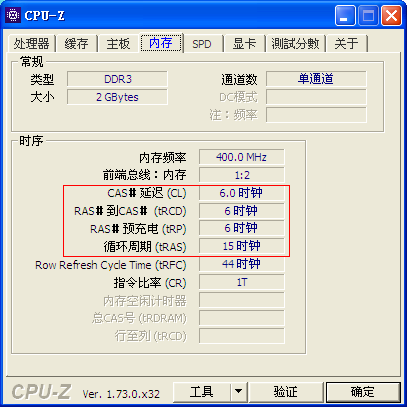

读取数据是内存最常见的操作之一。在DDR4内存中,读取数据的时序主要包括CAS延迟(CL)和列预充电时间(tRCD)。CAS延迟指的是从列地址被选中到数据可用之间的时间延迟,而列预充电时间则是在进行下一次读取之前需要等待多久。

写入数据的时序

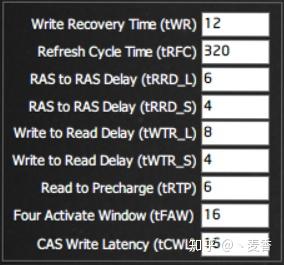

与读取数据类似,写入数据也需要一定的时间间隔。在DDR4内存中,写入数据的时序主要包括列地址选中时间(tCL)和写入延迟(WL)。列地址选中时间指的是从写入命令发出到列地址被选中之间的时间延迟,而写入延迟则是在进行下一次写入之前需要等待多久。