作为一名电子工程师,在设计和优化电路时,内存的时序数字传输是一个至关重要的考虑因素。在这篇文章中,我将分享我在实践中积累的经验,并提供一些有用的技巧来确保内存时序数字传输的稳定性和可靠性。

1.时序数字的选择与优化

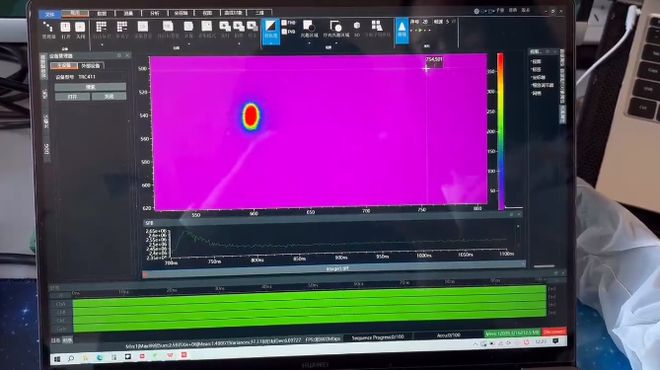

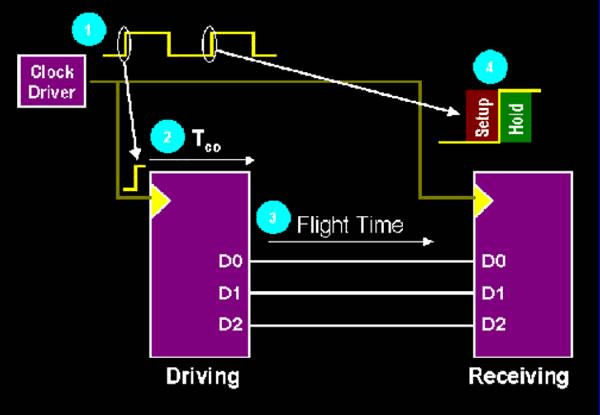

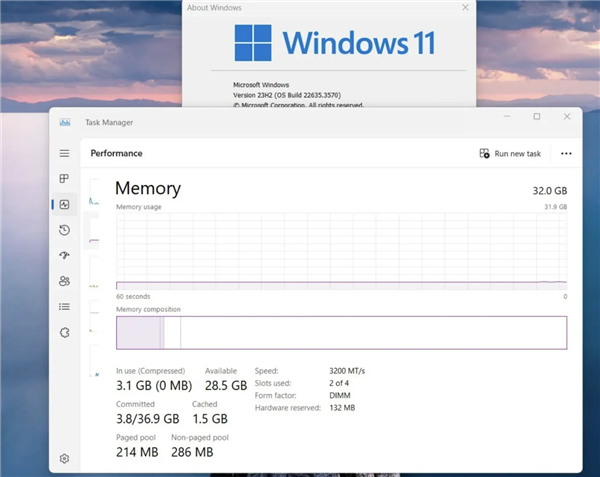

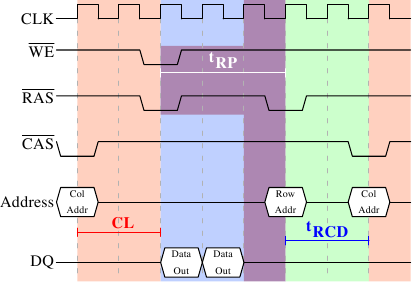

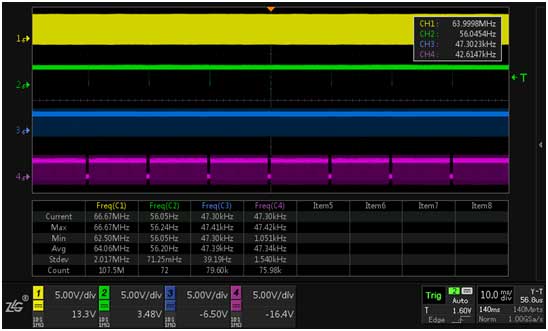

在设计中选择合适的内存时序数字是至关重要的。首先,我们需要根据系统需求和预算来确定所需的传输速度。然后,我们可以通过调整时钟频率、信号幅值和延迟等参数来优化时序数字。在此过程中,我们需要注意保持信号完整性和最小化干扰。

例如,在一个高性能计算系统中,我们可能需要高速数据传输,因此会选择较高的时钟频率和较短的延迟。然而,在一个功耗敏感的嵌入式系统中,我们可能需要降低时钟频率和增加延迟以节省功耗。因此,在选择和优化时序数字时,我们需要充分考虑系统需求和限制。

2.信号完整性的保障

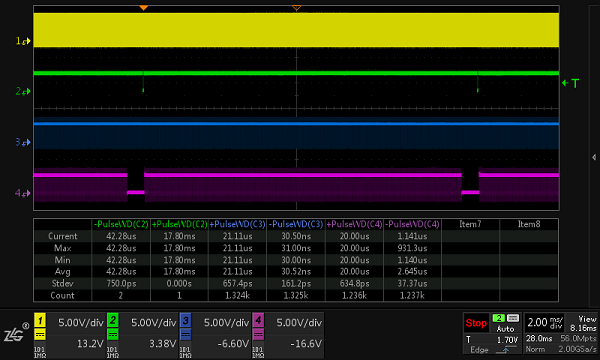

保持信号完整性对于内存时序数字传输至关重要。在设计中,我们需要注意以下几点来确保信号的质量和稳定性:

-电源和地线的布局:合理布局电源和地线,以最小化信号噪声和互相干扰。