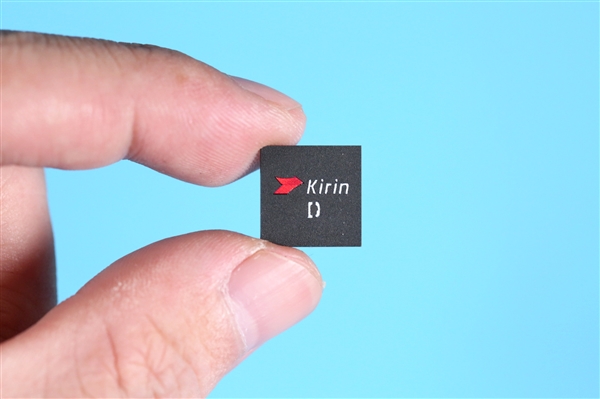

作为一名芯片设计工程师,我亲身经历了内存时序限制在2t的挑战。在这篇文章中,我将分享我的体验,并从三个方面来介绍这个问题。

挑战一:严苛的时间要求

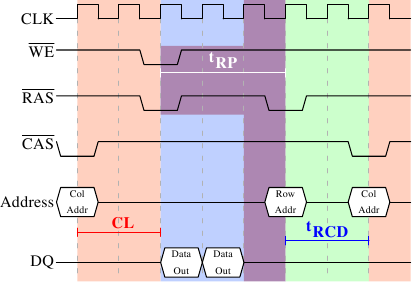

内存时序限制在2t意味着芯片的内存访问速度需要控制在一个非常短的时间范围内。对于我们芯片设计工程师来说,这是一项巨大的挑战。我们需要通过优化电路和设计来确保内存访问速度能够满足这个要求。我还记得当我第一次面对这个问题时,感到非常沮丧和无力。然而,通过不断地尝试和学习,最终我成功地解决了这个问题。

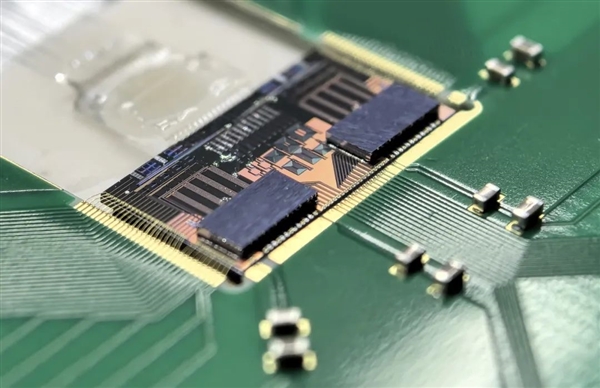

挑战二:复杂的电路设计

为了满足内存时序限制在2t的要求,我们需要设计复杂的电路来确保信号能够按时到达目标位置。这涉及到了时钟分配、延迟控制以及信号传输等方面的考虑。我曾经花费大量时间去优化电路布局,调整信号路径,并进行多次仿真和验证。每一次的尝试都让我更加了解电路设计的复杂性,也让我意识到自己的不断成长和进步。

挑战三:团队协作与沟通

在解决内存时序限制在2t的挑战中,团队协作和良好的沟通至关重要。