作为一名资深电子工程师,我曾经历过许多关于内存时序的挑战和探索。在这篇文章中,我将分享我在这个领域的经验和教训,希望对正在学习或从事相关工作的读者有所帮助。

一、时序设计的重要性

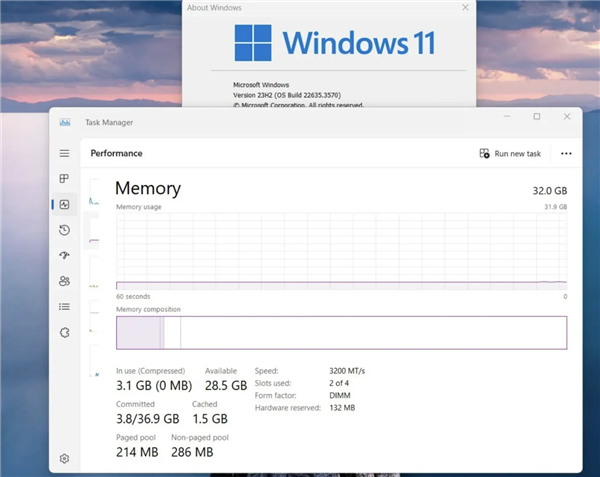

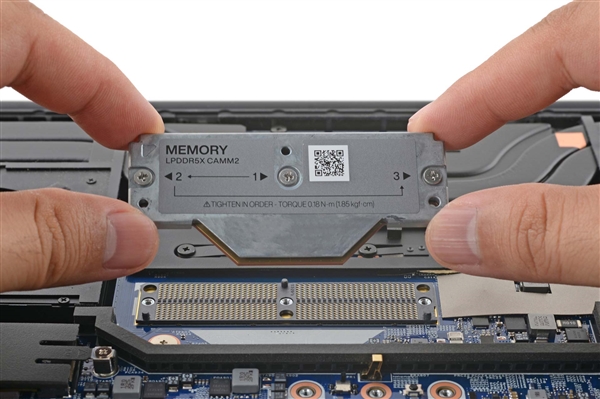

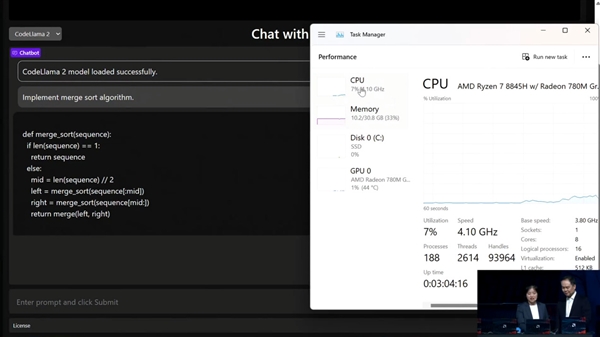

在现代电子设备中,内存时序设计是至关重要的。一个合理且稳定的时序设计可以提高系统性能,保证数据传输的准确性。然而,不少人在设计时序时往往忽视了其重要性。我曾经遇到过一个案例,在一个高性能计算机系统中,由于内存时序设计不合理,导致了频繁的数据错误和系统崩溃。通过对系统进行全面分析和优化,最终解决了这个问题。因此,在进行内存时序设计时,一定要充分考虑各种因素,并进行严密验证。

二、如何进行时序调试

在实际工作中,我们经常会遇到各种与内存时序相关的问题。当出现问题时,我们需要通过合理的调试方法来找出问题所在并解决。首先,我们要利用各种调试工具和仪器进行时序分析,例如逻辑分析仪、示波器等。其次,我们要对时序进行逐个信号的分析,找出潜在的问题点。最后,我们可以通过仿真和实验验证来进一步确认并解决问题。这个过程可能会耗费大量时间和精力,但只有通过不断地。